Guide to Six-Layer PCB Stackup Design

After exhausting the space on a 4-layer PCB, it's time to upgrade to a 6-layer circuit board. The additional layers offer space for more signals, extra planes, or a mix of conductors. The key isn't just having these extra layers but how to arrange them in the PCB stackup and how to route on a 6-layer PCB. If you've never used a 6-layer board before or encountered challenging stackup EMI issues, continue reading for some 6-layer PCB design guidelines and best practices.Why use 6 layers?

Before starting to build the board, I think it's important to consider the reasons why people might want to use a 6-layer PCB. There are several reasons beyond simply adding more paths for the signals.The most basic version of a 6-layer stack would use the same methodology as the SIG/PWR/GND/SIG stack in a 4-layer board, except that the signals would be placed on the other two in the center of the stack. In fact, the SIG/PWR/SIG/SIG/GND/SIG is the worst 6-layer PCB stack from an EMC standpoint, and it's probably only suitable for boards running at DC.

Some of the reasons I chose a 6-layer board over a 4-layer board include:

You are using a 4-layer SIG+PWR/GND/GND/SIG+PWR stack, and you need more space for components on the surface. Placing the PWR and SIG in the inner layers allows for more decoupling through the PWR/GND plane pair.

For mixed-signal boards, you can dedicate the entire surface layer to the analog interface and will have an additional internal layer for slower digital wiring.

You are using a high-speed board with a high I/O count and you want a good way to separate the signals into different layers of the board. You can implement the same strategy in #1.

In all of these configurations, only one additional signal layer is added. The other layer is dedicated to the GND plane, the power rails, or the full power plane. Your stacking layer will be the main determinant of EMC and signal integrity in the board as well as layout and routing strategy.

In this stack, the top and bottom layers sit on a thin dielectric, so these layers should be used for impedance control signals. 10 mils is probably the thickest dielectric you should use, as this will require the use of microstrip routing with a width of 15-20 mils, depending on the dielectric constant. If you are wiring a digital interface with differential pairs, the spacing will also allow you to reduce the width of the traces, which will allow you to wire into finer-pitch components. As an example, we use a version of the above stack for many of our smaller networking products that support multiple multi-gigabit Ethernet channels.

If you need to use smaller trace widths in the outer layer, simply reduce the outer dielectric thickness (perhaps as low as 4-5 mils) and then add some thickness to the L3-L4 dielectric to meet your board thickness goals. The next point to consider is how to route the power supply.

How to Wire a Power Supply?

In the above example of a 6 layer PCB stack, there is an entire layer dedicated to the PWR. in a 6 layer PCB, this is usually a good practice as it frees up the surface area for components and makes it easier to power these components through the via holes.

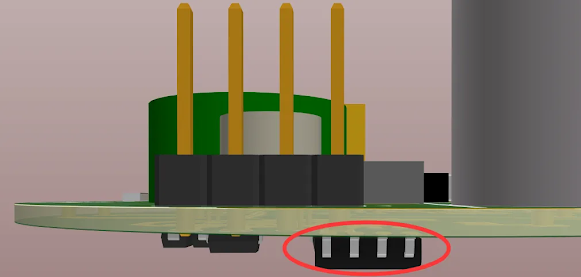

Just as an example, take a look at the BGA shown below. this particular BGA is typical of high speed interface controllers that need to supply a lot of current at multiple voltages, so many of the balls will be connected to power and ground. With something like an FPGA, you may find multiple pins for power and ground throughout its package. By dedicating a single layer to the power supply, you can break up the plane into tracks so that multiple voltages can be used at high currents if necessary. This eliminates the need to overlap these power rails at different voltages, preventing additional EMI issues.

.webp)

Comments

Post a Comment