Introduction to Intel's PCB Tabbed Routing Technology and Solutions

1. What is Tabbed Routing

Tabbed Routing is an innovative PCB routing method invented by Intel, targeting the limited PCB routing area, which cannot meet the normal transmission line width and spacing requirements between lines, thus generating impedance mismatch and signal crosstalk. Tabbed Routing can be applied to any bus in theory, but based on the wiring characteristics of various buses, DDR bus is the main application scenario at present. Tabbed Routing can be applied to any bus in theory, but based on the wiring characteristics of various buses, DDR is the main application scenario.

2. Why use Tabbed Routing?

To answer this question, you need to understand the cabling characteristics of the DDR bus and a few key concepts: Pin Field, Breakout, Open Field, etc. Intel PDG uses these terms to describe different cabling areas, of course, there are terms to describe other areas, but this article only discusses Tabbed Routing-related applications, which involve the following three parts But this article only discusses the application of Tabbed Routing, which involves these 3 parts.

First of all, let's take a look at the overall schematic of DDR PCB routing, which can be roughly divided into three parts: the CPU area, the routing area, and the DIMM connector or DRAM area.

The CPU area and some wiring areas are expanded and refined, and a design is shown below. For this PCB design, it is assumed that the transmission line impedance requirement is 40 ohms, the corresponding line width is 6 mils, and the PDG compliant line spacing is 18 mils.

Pin Field refers to the CPU / BGA area BGA Ball and the corresponding area of the hole, this area is characterized by PCB space is BGA Pad, Pad leads out of the hole is greatly occupied, so the transmission line routing area will become relatively small, in order to be able to put the signal line out of the limited area, it is inevitable that need to use the line width is thin, the spacing of the completion of the signal out of the line in a smaller way, the following figure shows a PCB surface layer impedance requirements of 40 ohms, the corresponding line width of 6 mil, meet the PDG requirements of 18 mil spacing. The following figure for a PCB surface wiring example, here the transmission line width can only be 3.5 mil, relative to the normal line width of 6 mil, the impedance will inevitably become larger, then in the entire signal link, is an impedance discontinuity; another aspect, the line spacing will be more uneven, but relative to the normal wiring will be smaller, such as 4 mil, then relative to the normal spacing of the line 18 mil, the crosstalk will increase.

Pin field has another form, for the inner layer stripline, for multi-channel DDR cabling, BGA area alignment depth will be deeper, can only be passed from each Via, and generally between the two Via can only be passed through a pair of two width of about 3.5 mil, spacing of 4 mil, so its impedance will be larger, if it is more desirable stripline, let's say its far-end crosstalk is relatively small.

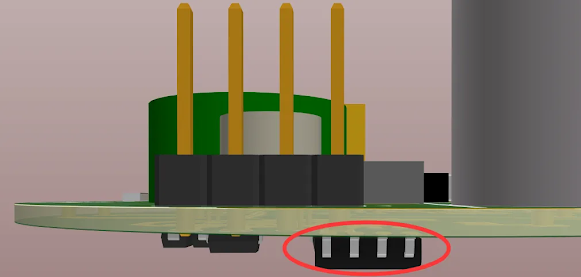

Pin Field after a section of the line, known as Breakout, which is characterized by a complete wiring space, but because the DDR signal line is dense, need a section of the area will be fanning out, so the Breakout area is also a relatively limited space, the general use of the line width of 4 mil, spacing of 8 mil for the way to the line, compared to the normal line width of 6 mil, spacing 18 mil normal alignment, its impedance and crosstalk is also relatively large. Compared with the normal line width of 6 mil, spacing 18 mil of normal alignment, its impedance and crosstalk is also relatively large.

After Breakout, after the fan out of this area, there can be a whole piece of area can be wired, this is called Open Field, that is, according to the design rules, the normal wiring of the area, this example, the line width of 6 mil, line spacing of 18 mil.

For DDR design, signal reflection and crosstalk are the two biggest problems, so engineers and designers have to do everything possible to make the impedance as consistent or close as possible, and crosstalk as small as possible.

Corresponding to the PCB design, the conventional method, is to use as much as possible the normal line width and line spacing for wiring, that is to say, to reduce the length of the Pin Field and Breakout area (ideally, all the way to use the Open Field), but it is more difficult to realize, and the overall Cost will rise dramatically, because it requires more layers of wiring to complete the BGA region out of the line.

Therefore, in the Pin Field and Breakout region of the wiring length can not be reduced in the case, Intel proposed Tabbed Routing routing, through these areas, to add some Tab, to compensate for the consistency of the impedance, as well as to reduce the crosstalk at the far end.

2. Why use Tabbed Routing?

According to the above, Tabbed Routing serves 2 main purposes:

Reduce the impedance of this area, so that the impedance matching is better, thus reducing the signal reflection.

Reduce crosstalk between signals, more accurately, is to reduce crosstalk at the far end.

For the first point, more intuitive, increase the Tab, in fact, to a certain extent, increase the line width, so its impedance will become smaller, and the normal alignment of the impedance closer.

For reducing crosstalk between signals at the far end, a common pair of coupled lines as shown below:

The equivalent circuit and the schematic of the remote crosstalk are shown below:

The magnitude of the crosstalk that can be crosstalked from its far end can be expressed by the following equation [1], noting that the even and odd modes of the signal will be considered here.

Comments

Post a Comment